Clock domain crossing errors are impossible to simulate in old Verilog simulators, the reason being that signals are processed sequentially and can only have 0/1 values, so can never be coincident. Consequently most CDC tools only do static analysis.

Back around 2000 a company came up with a way of simulating variable timing called “histogram simulation”, it did min/typ/max timing all at one go.

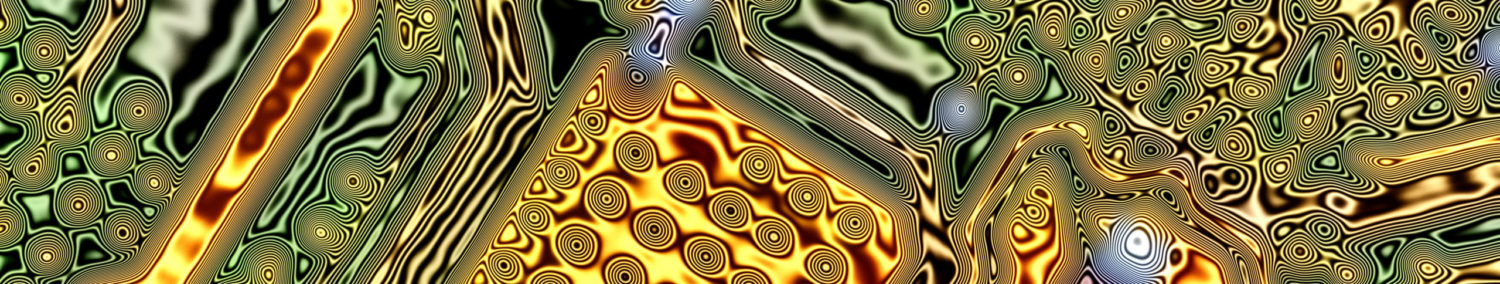

An extension of the concept is to do continuous logic-level probability modeling. In simulation that looks like analog waveforms that transition between levels of absolute certainty. Where there are coincident non-absolute levels there is a CDC or timing problem.

Cameron EDA holds the patent for the approach –

Including variability in simulation of logic circuits

It works with UVM (constrained random testing), by just using different models.